автордың кітабын онлайн тегін оқу Проектирование от печки — Трассировка высокоскоростных цифровых печатных плат

Проектирование от печки — Трассировка высокоскоростных цифровых печатных плат

12+

Оглавление

Предисловие

Фразы обведенные в рамочки рекомендуется зазубрить. Это сформирует интуитивное понимание сути процессов «на ходу».

Практика

Задание основных правил трассировки

Классы цепей

Импедансы

Для современных высокоскоростных цифровых печатных плат (ВЦПП) характерно преобладание PCIe среди ВЧ интерфейсов. Логично, чтобы дифпары 85 Ом были минимального размера (100/100 или 75/75 мкм).

Раскрашивание

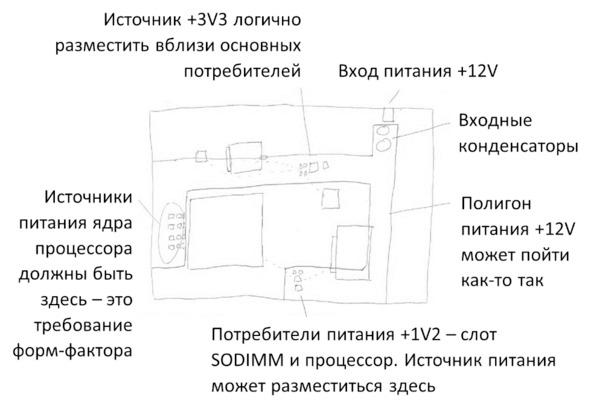

Расстановка всех компонентов

Предварительная отрисовка полигонов питания